|

foxBMS

1.1.0

The foxBMS Battery Management System API Documentation

|

|

foxBMS

1.1.0

The foxBMS Battery Management System API Documentation

|

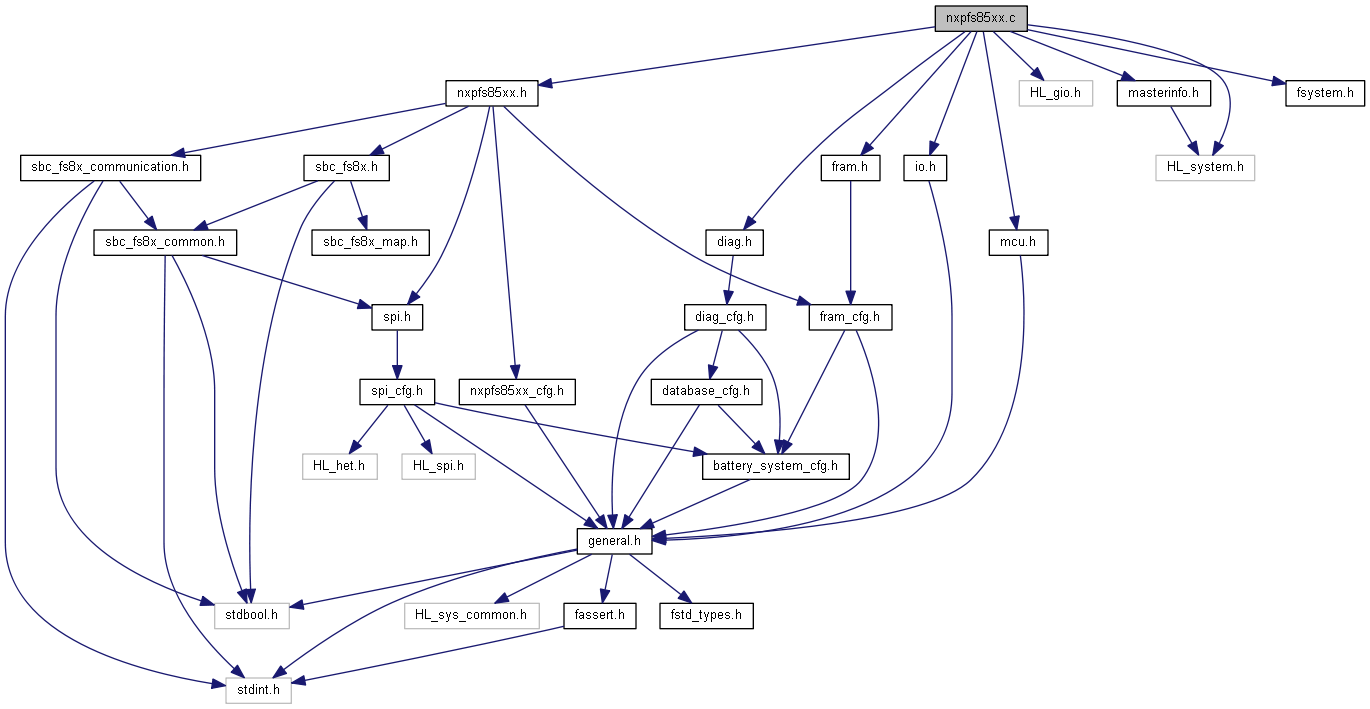

Driver for the SBC module. More...

#include "nxpfs85xx.h"#include "HL_gio.h"#include "HL_system.h"#include "diag.h"#include "fram.h"#include "fsystem.h"#include "io.h"#include "masterinfo.h"#include "mcu.h"

Go to the source code of this file.

Typedefs | |

| typedef enum SBC_INIT_PHASE | SBC_INIT_PHASE_e |

Enumerations | |

| enum | SBC_INIT_PHASE { SBC_UNINITIALIZED , SBC_FIN_TEST , SBC_RSTB_ASSERTION_TEST , SBC_INITIALIZED } |

Functions | |

| static STD_RETURN_TYPE_e | SBC_CheckRegisterValues (uint32_t registerValue, uint32_t expectedRegisterValue) |

| Checks register value against expected value. More... | |

| static void | SBC_UpdateRegister (FS85xx_STATE_s *pInstance, bool isFailSafe, uint32_t registerAddress, uint32_t registerValue) |

| Updates register values. More... | |

| static STD_RETURN_TYPE_e | SBC_ReadBackRegister (FS85xx_STATE_s *pInstance, bool isFailSafe, uint8_t registerAddress) |

| Reads SBC register value. More... | |

| static STD_RETURN_TYPE_e | SBC_WriteRegisterFsInit (FS85xx_STATE_s *pInstance, uint8_t registerAddress, uint16_t registerValue) |

| Write to fail-safe register. More... | |

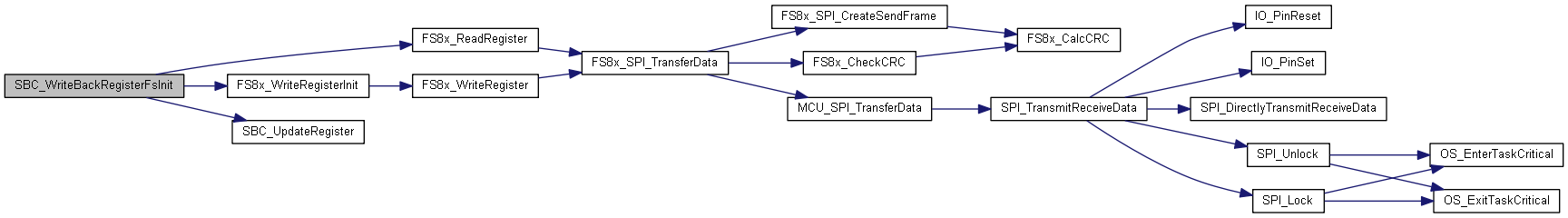

| static STD_RETURN_TYPE_e | SBC_WriteBackRegisterFsInit (FS85xx_STATE_s *pInstance, uint8_t registerAddress, uint16_t registerValue) |

| Write to fail-safe register. More... | |

| static STD_RETURN_TYPE_e | SBC_ClearRegisterFlags (FS85xx_STATE_s *pInstance, uint8_t registerAddress, bool isFailSafe, uint16_t registerValue) |

| Clears flags in register. More... | |

| static STD_RETURN_TYPE_e | SBC_ReadBackAllRegisters (FS85xx_STATE_s *pInstance) |

| static STD_RETURN_TYPE_e | SBC_PerformPathCheckRSTB (FS85xx_STATE_s *pInstance) |

| Perform RSTB safety path check. More... | |

| static STD_RETURN_TYPE_e | SBC_PerformPathCheckFS0B (FS85xx_STATE_s *pInstance) |

| Perform FS0B safety path check. More... | |

| STD_RETURN_TYPE_e | FS85X_InitFS (FS85xx_STATE_s *pInstance) |

| Configures SBC during INIT_FS phase. More... | |

| STD_RETURN_TYPE_e | FS85X_Init_ReqWDGRefreshes (FS85xx_STATE_s *pInstance, uint8_t *requiredWatchdogRefreshes) |

| Calculates the number of required watchdog refresh to reset fault error counter. More... | |

| STD_RETURN_TYPE_e | FS85X_CheckFaultErrorCounter (FS85xx_STATE_s *pInstance) |

| Checks if fault error counter is zero. More... | |

| STD_RETURN_TYPE_e | FS85X_SafetyPathChecks (FS85xx_STATE_s *pInstance) |

| Performs SBC safety path checks. More... | |

| UNIT_TEST_WEAK_IMPL fs8x_status_t | MCU_SPI_TransferData (SPI_INTERFACE_CONFIG_s *pSpiInterface, uint8_t *txFrame, uint16_t frameLengthBytes, uint8_t *rxFrame) |

| This function transfers single frame through blocking SPI communication in both directions. MCU specific. More... | |

| STD_RETURN_TYPE_e | SBC_TriggerWatchdog (FS85xx_STATE_s *pInstance) |

| Trigger watchdog. More... | |

Variables | |

| FS85xx_STATE_s | fs85xx_mcuSupervisor |

Driver for the SBC module.

SPDX-License-Identifier: BSD-3-Clause

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

We kindly request you to use one or more of the following phrases to refer to foxBMS in your hardware, software, documentation or advertising materials:

It must always be used when creating new c source files.

Definition in file nxpfs85xx.c.

| typedef enum SBC_INIT_PHASE SBC_INIT_PHASE_e |

| enum SBC_INIT_PHASE |

| Enumerator | |

|---|---|

| SBC_UNINITIALIZED | |

| SBC_FIN_TEST | |

| SBC_RSTB_ASSERTION_TEST | |

| SBC_INITIALIZED | |

Definition at line 72 of file nxpfs85xx.c.

| STD_RETURN_TYPE_e FS85X_CheckFaultErrorCounter | ( | FS85xx_STATE_s * | pInstance | ) |

Checks if fault error counter is zero.

| [in,out] | pInstance | SBC instance where fault error counter is checked |

Definition at line 898 of file nxpfs85xx.c.

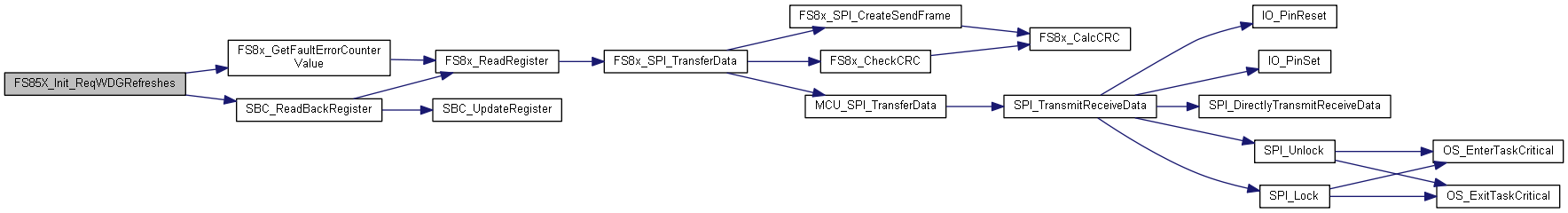

| STD_RETURN_TYPE_e FS85X_Init_ReqWDGRefreshes | ( | FS85xx_STATE_s * | pInstance, |

| uint8_t * | requiredWatchdogRefreshes | ||

| ) |

Calculates the number of required watchdog refresh to reset fault error counter.

| [in,out] | pInstance | SBC instance that is initialized |

| [out] | requiredWatchdogRefreshes | number of required good watchdog refreshes |

Clear the fault error counter to 0 with consecutive good WD refreshes. The watchdog refresh counter is used to decrement the fault error counter. Each time the watchdog is properly refreshed, the watchdog refresh counter is incremented by '1'. Each time the watchdog refresh counter reaches its maximum value ('6' by default) and if next WD refresh is also good, the fault error counter is decremented by '1'. Whatever the position the watchdog refresh counter is in, each time there is a wrong refresh watchdog, the watchdog refresh counter is reset to '0'.

Read out FS_I_WD_CFG register to get watchdog refresh counter limit and value

Get refresh counter value

Get refresh counter limit register value

Get fault error counter

Get number of required watchdog refreshes to clear fault error counter to 0

Definition at line 844 of file nxpfs85xx.c.

| STD_RETURN_TYPE_e FS85X_InitFS | ( | FS85xx_STATE_s * | pInstance | ) |

Configures SBC during INIT_FS phase.

Checks first if SBC currently is in INIT_FS phase and if not transfers SBC back into INIT_FS. Verifies basic checks, configures fail-safe registers and closes INIT_FS afterwards.

| [in,out] | pInstance | SBC instance that is initialized |

First: Verify following conditions:

Second: Configure FS_I and FS_I_NOT registers

Third: Execute

The FS85 is now ready. If everything is OK for the MCU, it can release its own safety path and the ECU starts.

1.: Verify LBIST and ABIST1

Read FS STATES register

2.: Check if debug mode is active

3.: Verify that no OPT CRC error

-----— Second: Configure fail-safe init registers ---------------—

Check if SBC is in FS_INIT state, if not switch SBC in FS_INIT state. Specific configurations can only be done in FS_INIT state

1.: Configure VCOREMON_OV_UV impact on RSTB and FS0B

2.: Configure VDDIO_OV_UV impact on RSTB and FS0B

4.: Configure ABIST2 assignment

Select VCOREMON_OV options:

Select VCOREMON_UV options:

Select VDDIO_OV options:

Select VDDIO_UV options:

Select ABIST2 options:

3.: Configure VMONx_OV_UV impact on RSTB and FS0B

Select VMONx_OV options:

Select VMONx_UV options:

5.: Configure the WD window period, the WD window duty cycle, the WD counters limits, and its impact on RSTB and FS0B. Ensure that the configuration does not violate the FTTI requirement at system level.

WD window period options:

WD window duty cycle options:

WD fault recovery strategy

6.: Configure the Fault Error Counter limit and its impact on RSTB and FS0B at intermediate value

Configure the RSTB pulse duration

Configure FS0B short to high impact on RSTB

Fault Error Counter limit options:

Fault Error Counter impact options:

7.: RSTB pulse duration options:

10.: FS0B short to high impact on RSTB options:

After POR fault-error counter is set to 1 on default, it is reset after two consecutive good WD refreshes. This part of the register is read-only so a write access has no influence. Set this bit for a successful comparison between written and read register value

8.: Configure MCU FCCU error monitoring and its impact on RSTB and FS0B

9.: Configure Ext. IC error monitoring and its impact on RSTB and FS0B

MCU FCCU error monitoring options:

Ext. IC error monitoring options:

1.: Close INIT_FS by sending the first good WD refresh

2.: Execute ABIST2 and verify it is pass

ABIST2 is executed automatically after closing of INIT_FS, duration: 1.2ms max

3.: Clear all the flags by writing in FS_DIAG_SAFETY

Flags are cleared by writting '1' to register

Clear all the flags by writing in FS_OVUVREG_STATUS

Flags are cleared by writting '1' to register

Clear flags FLAG1 register

Clear flags FLAG2 register

Read out all registers for debug purpose

Definition at line 461 of file nxpfs85xx.c.

| STD_RETURN_TYPE_e FS85X_SafetyPathChecks | ( | FS85xx_STATE_s * | pInstance | ) |

Performs SBC safety path checks.

Function perform safety path checks for FIN, FS0B and RSTB to ensure that all pins work as expected

| [in,out] | pInstance | where the safety paths are checked |

Definition at line 910 of file nxpfs85xx.c.

|

static |

Checks register value against expected value.

If actual register value equals expected value STD_OK is returned if this is not the case this indicates an error and STD_NOT_OK is returned.

| [in] | registerValue | actual register value of interest |

| [in] | expectedRegisterValue | expected register value |

Definition at line 205 of file nxpfs85xx.c.

|

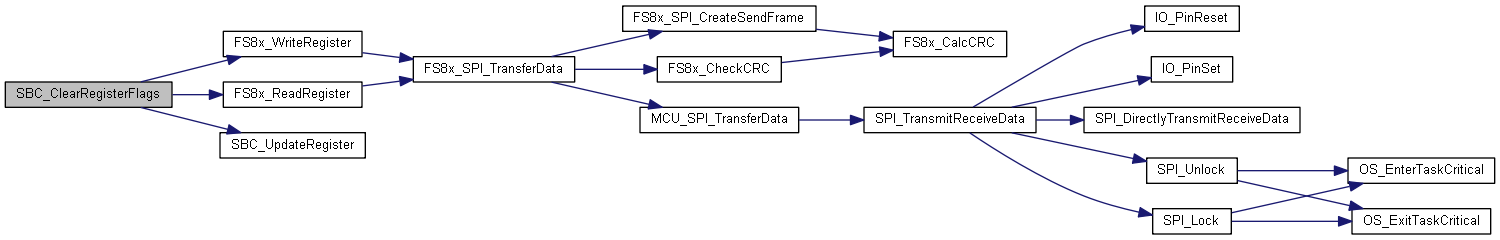

static |

Clears flags in register.

Writes to register, reads back if clear process was successful and afterwards updates register value of passed SBC instance

| [in,out] | pInstance | SBC instance that is updated |

| [in] | registerAddress | address of register |

| [in] | isFailSafe | true if fail-safe register, false if main register |

| [in] | registerValue | value that is written into register |

Definition at line 426 of file nxpfs85xx.c.

|

static |

Perform FS0B safety path check.

This functions performs a safety path check to make sure external components connected to FS0B are available to bring the safety critical outputs to known levels during operation.

| [in,out] | pInstance | SBC instance for which the FS0B path is checked |

Definition at line 1176 of file nxpfs85xx.c.

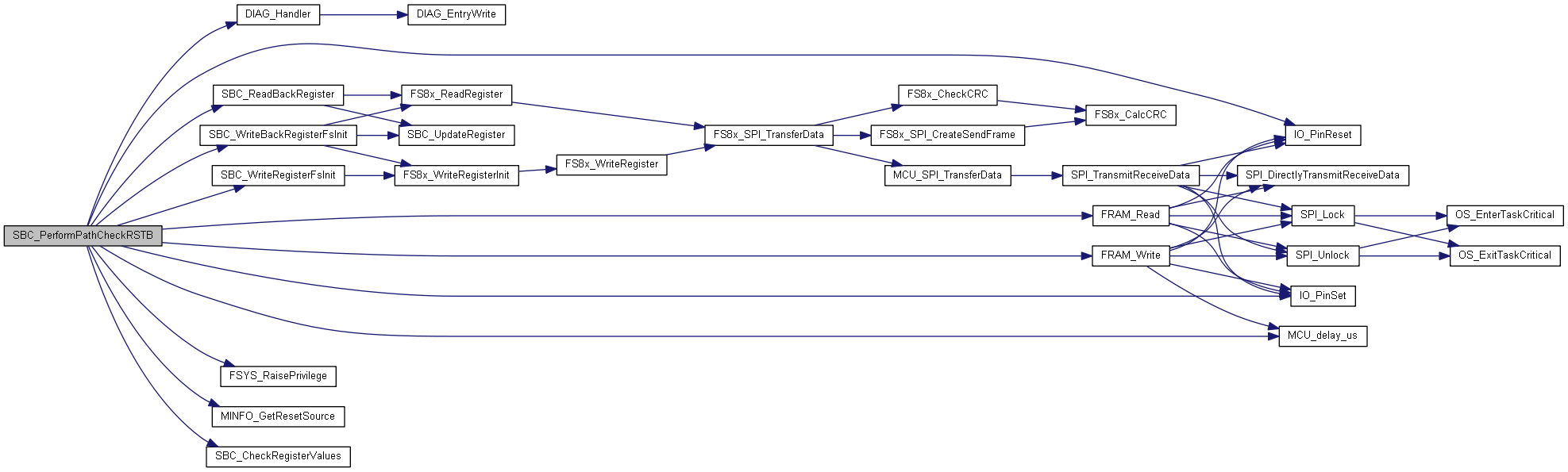

|

static |

Perform RSTB safety path check.

This functions performs a safety path check to make sure external components connected to RSTB are available to bring the safety critical outputs to known levels during operation.

| [in,out] | pInstance | SBC instance for which the RSTB path is checked |

Assertion of RSTB pin will trigger reset, check if reset reason was power-cycle. If so, check if short circuit between FIN and RSTB pin exists

First check if FIN is used

Write to NVRAM to determine after reset and if short-circuit between RSTB and FIN present what exactly caused the reset.

MCU SBC is connected to ECLK1 -> privilege mode is required to access register

Last reset was caused by power-cycle

Set level of FIN pin low and check if this generates reset

Pulses longer than 2000ns trigger reset -> wait 10us to check if reset is triggered by short between RSTB and FIN

If we reach this line of code, no reset has taken place. Everything okay. Set level of FIN pin back to high

No further register access required -> leave privilege mode

FIN state okay, no short circuit. Update also in nvram struct

Continue with RSTB assertion test

Power-cycle but no FIN pin used -> continue with RSTB check

Last reset reason was external reset via nRST pin (EXT_RESET) Readout FRAM to determine in which state the SBC was prior to reset

Short-circuit between FIN and RSTB: Do not apply CLK on FIN

Update nvram FIN state

FIN state not okay, but still in SBC init phase after power-cycle continue now with RSTB assertion

Reset was triggered by SPI RSTB assertion test -> continue with SBC init phase

Diagnosis of the RSTB pin/event is available by reading the FS_SAFE_IOs register: RSTB_EVENT bit reports an activation of RSTB pin.

Check RSTB_EVENT if RSTB has been activated

RSTB pin should be sensed high and no RSTB short to high

Reset RSTB_EVENT flag

Update diag flag

RSTB has not been activated but this should have been the case

Reset was not caused by SBC initialization or power-cycle. Continue with SBC init phase as RSTB assertion is only tested after power-cycle occurred

Copy FIN state info from nvram variable into local state variable. This restores lost data from rest or updates local FIN state if short-circuit between FIN and RSTB has been detected

Reset was not caused by power-cycle or SBC. SBC has already been initialized successfully after detected power-cycle. Everything okay. Read FIN state from NVRAM and continue with normal operation

Verify the hardware connection between the MCU reset pin and the FS85 reset pin

Write to NVRAM to determine after reset and if RSTB was asserted correctly

Definition at line 1045 of file nxpfs85xx.c.

|

static |

|

static |

Reads SBC register value.

Reads SBC register value from registerAddress and updates register in SBC state variable if reading was successful

| [in,out] | pInstance | SBC instance that is updated |

| [in] | isFailSafe | true if fail-safe register, false if main register |

| [in] | registerAddress | address of register that is read from |

Definition at line 362 of file nxpfs85xx.c.

| STD_RETURN_TYPE_e SBC_TriggerWatchdog | ( | FS85xx_STATE_s * | pInstance | ) |

Trigger watchdog.

Triggers watchdog of passed SBC instance and verify if it was good refresh within the configured window

| [in,out] | pInstance | SBC instance where the watchdog is triggered |

Definition at line 973 of file nxpfs85xx.c.

|

static |

Updates register values.

Updates register value of passed SBC instance with new values

| [in,out] | pInstance | SBC instance that is updated |

| [in] | isFailSafe | true if fail-safe register, false if main register |

| [in] | registerAddress | address of register that is updated |

| [in] | registerValue | register value |

Definition at line 213 of file nxpfs85xx.c.

|

static |

Write to fail-safe register.

Writes to fail-safe register (can be done during FS_INIT phase only), reads back if write process was successful and afterwards updates register value of passed SBC instance

| [in,out] | pInstance | SBC instance that is updated |

| [in] | registerAddress | address of register |

| [in] | registerValue | value that is written into register |

Definition at line 396 of file nxpfs85xx.c.

|

static |

Write to fail-safe register.

Writes to fail-safe register (can be done during FS_INIT phase only)

| [in] | pInstance | SBC instance that is updated |

| [in] | registerAddress | address of register |

| [in] | registerValue | value that is written into register |

Definition at line 378 of file nxpfs85xx.c.

| FS85xx_STATE_s fs85xx_mcuSupervisor |

Definition at line 80 of file nxpfs85xx.c.