6.3.2. Interface MAX17841B v1.0.0

6.3.2.1. Overview

Important

The following description only applies for the Maxim MAX17841B-based

BMS-Interface Board hardware version 1.0.0.

Hint

All connector pinouts described below follow the Convention for Molex Micro-Fit 3.0 Connector Pin Numbering and Convention for Samtec Edge Rate connectors.

The BMS-Interface Board is used to enable communication between the BMS-Master Board and the BMS-Slave Boards. A 3D rendering from the TOP side view of the BMS-Interface Board is shown in Fig. 6.4. The BMS-Interface Board is intended to be used together with a BMS-Master Board.

Fig. 6.4 3D rendering of the BMS-Interface Board

6.3.2.2. Specifications

6.3.2.2.1. Mechanical Dimensions

The size of the PCB is 70 mm x 120 mm. A 3D-model and a drawing of the PCB can be found in Design Resources

6.3.2.2.2. Battery Management UART Insulation

The interface board is designed for a maximum continuous insulation voltage of 1250 V DC between all two Maxim Battery Management UART channels and between each Maxim Battery Management UART channel and the BMS-Master Board.

The insulation is designed according to DIN EN 60664-1:2008-01 under the following conditions:

Type of insulation: functional

Electrical field: homogeneous

Pollution degree: 2

PCB insulator class: 3b

Transient voltage: 4300 V DC

Continuous (working) voltage: 1250 V DC (selected due to design space constraints on PCB)

The PCB design complies with the following parameters:

Clearance: 1.3 mm

Creepage distance: 12.5 mm

6.3.2.2.3. Block Diagram

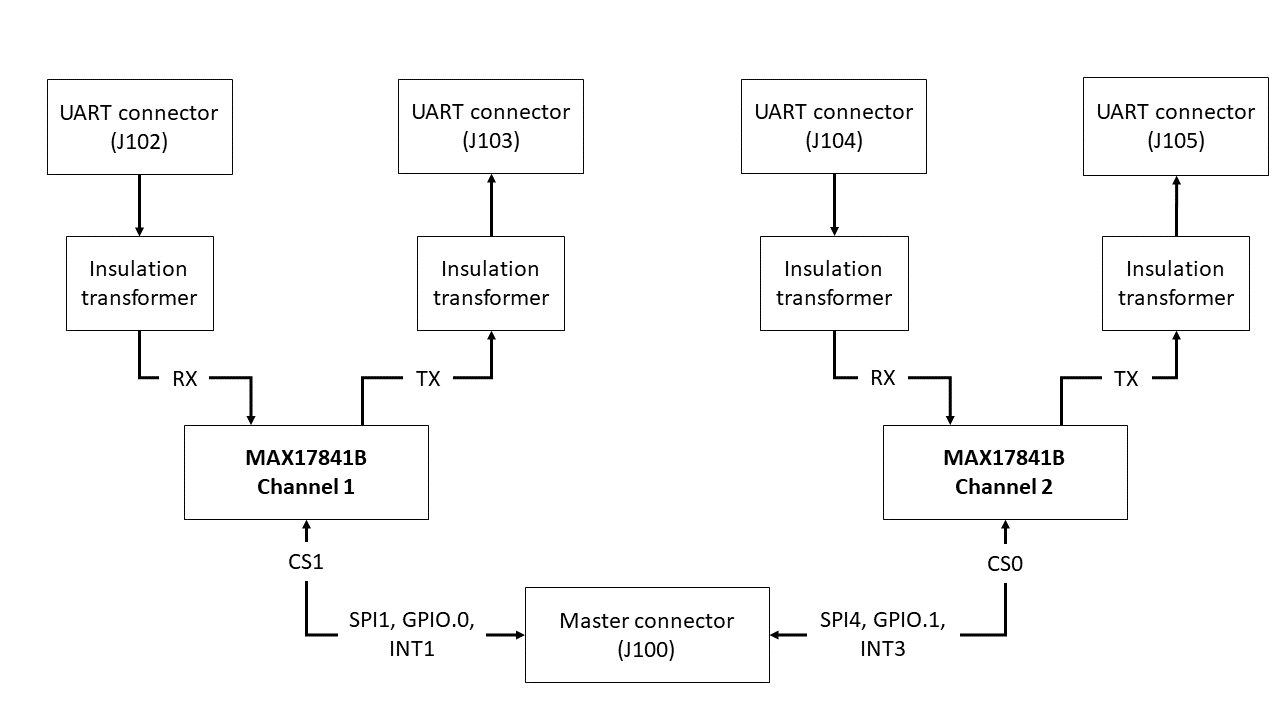

A block diagram of the BMS-Interface Board is shown in Fig. 6.5.

Fig. 6.5 Block diagram of the BMS-Interface Board

Each Maxim MAX17841B communication chip from Maxim Integrated provides one UART channel. Each channel is comprised of a RX and a TX signal, each using one insulation transformer. The Maxim MAX17841B chips are directly connected to the MCU via SPI.

6.3.2.2.4. Schematic and Board Layout

More information about the board schematic and layout files can be found in section Design Resources. For better debugging, there are test-points on the PCB for all relevant IO signals. In addition to test-points, a pin header (J101) allows an easier connection to a logic analyzer.

6.3.2.3. Functions

6.3.2.3.1. Maxim Battery Management UART communication

The BMS-Interface Board offers up to two isolated Maxim Battery Management UART communication channels using the Maxim MAX17841B transceiver chip from Maxim Integrated. The Maxim MAX17841B transceivers are controlled by the SPI signals from the BMS-Master Board. The UART RX signals are available on the connectors J102 and J104. The pinout of the connectors is described in Table 6.3.

Pin |

Signal |

Description |

|---|---|---|

1 |

UART_RX_p |

UART RX positive |

2 |

UART_RX_n |

UART RX negative |

The UART TX signals are available on the connectors J103 and J105. The pinout of the connectors is described in Table 6.4.

Pin |

Signal |

Description |

|---|---|---|

1 |

UART_TX_p |

UART TX positive |

2 |

UART_TX_n |

UART TX negative |

For the connection to the BMS-Master Board, a 40-pole mezzanine connector (J100) is used. The pinout and pin usage is described in Table 6.5

Pin |

Signal |

Description |

Usage on BMS-Interface Board |

|---|---|---|---|

1 |

|

- |

UART channel 1 |

2 |

|

- |

- |

3 |

|

- |

UART channel 1 |

4 |

|

- |

- |

5 |

|

- |

UART channel 1 |

6 |

|

- |

UART channel 1 |

7 |

|

- |

- |

8 |

|

- |

- |

9 |

|

- |

- |

10 |

|

- |

- |

11 |

|

- |

UART channel 2 |

12 |

|

- |

UART channel 2 |

13 |

|

- |

UART channel 2 |

14 |

|

- |

UART channel 2 |

15 |

|

- |

- |

16 |

|

- |

- |

17 |

|

- |

- |

18 |

|

- |

- |

19 |

|

- |

- |

20 |

|

Interrupt pin, connected to MCU GIOA_2 |

UART channel 1 [max17841b] interrupt |

21 |

|

Interrupt pin, connected to MCU GIOA_3 |

UART channel 1 [max17841b] enable |

22 |

|

Interrupt pin, connected to MCU GIOA_4 |

UART channel 2 [max17841b] interrupt |

23 |

|

Interrupt pin, connected to MCU GIOA_6 |

UART channel 2 [max17841b] enable |

24 |

|

GPIO pin, connected to port expander 3 IO1_0 |

UART channel 1 [max17841b] enable |

25 |

|

GPIO pin, connected to port expander 3 IO1_1 |

UART channel 2 [max17841b] enable |

26 |

|

GPIO pin, connected to port expander 3 IO1_2 |

- |

27 |

|

GPIO pin, connected to port expander 3 IO1_3 |

- |

28 |

|

GPIO pin, connected to port expander 3 IO1_4 |

- |

29 |

|

GPIO pin, connected to port expander 3 IO1_5 |

- |

30 |

|

GPIO pin, connected to port expander 3 IO1_6 |

- |

31 |

|

GPIO pin, connected to port expander 3 IO1_7 |

- |

32 |

|

Power supply ground |

Power supply ground |

33 |

|

Power supply ground |

Power supply ground |

34 |

|

3.3 V from peripheral SBC |

3.3 V power supply |

35 |

|

3.3 V from peripheral SBC |

3.3 V power supply |

36 |

|

5.0 V from peripheral SBC |

- |

37 |

|

5.0 V from peripheral SBC |

- |

38 |

|

12 V from buck-boost converter |

- |

39 |

|

Master supply voltage (after protection circuits) |

- |

40 |

|

Master supply voltage (after protection circuits) |

- |

All important IO signals are connected to a pin header (J101) to provide an easy connection to a logic analyzer. The pinout of this header is described in Table 6.6

Pin |

Signal |

Description |

|---|---|---|

1 |

|

- |

2 |

|

- |

3 |

|

UART channel 2 |

4 |

|

UART channel 1 |

5 |

|

UART channel 2 |

6 |

|

UART channel 1 |

7 |

|

UART channel 2 |

8 |

|

UART channel 1 |

9 |

|

UART channel 2 |

10 |

|

UART channel 1 |

11 |

|

UART channel 2 [max17841b] interrupt |

12 |

|

UART channel 1 [max17841b] interrupt |